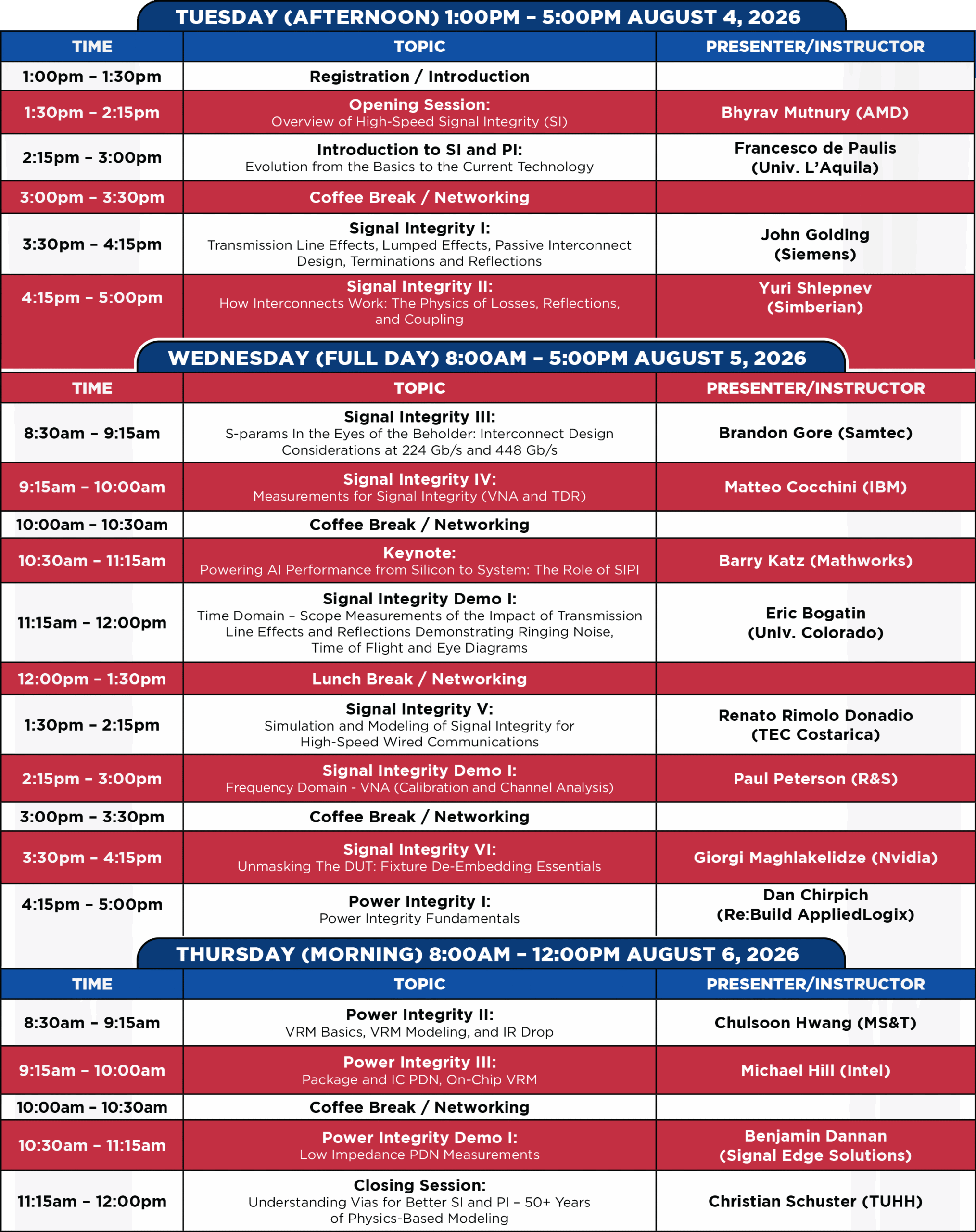

Global SIPI University

3rd Signal Integrity and Power Integrity (SIPI)

Global University

Tuesday – Wednesday – Thursday, August 4 – 6, 2026

Fee: $325 Advance/ $380 Regular

2026 IEEE International Symposium on EMC+SIPI in Dallas, Texas

The Organizing Committee of the 2026 IEEE International Symposium on Electromagnetic Compatibility and Signal & Power Integrity (EMC+SIPI) is planning to offer a high-quality, educational event encompassing Signal Integrity (SI) and Power Integrity (PI): the Global Signal Integrity and Power Integrity University.

Similar to the Clayton R. Paul Global EMC University that is held annually during the International Symposium, the intent is to offer two full days of lectures (Tuesday afternoon, all day Wednesday, and Thursday morning) carefully curated to cover basic and advanced concepts of SI & PI during the symposium week. SI & PI are gaining ever-growing attention due to the higher data rates and larger currents in modern high-speed digital systems. Industry requires skilled engineers with a background in these two disciplines to address the increasing complexity and challenges of electronic system design.

The IEEE EMC Society therefore decided to offer again – after the first two successful editions at the Symposium in Phoenix, Arizona (2024) and Raleigh, North Carolina (2025) – two full days of courses during the EMC+SIPI Symposium 2026 to bridge this gap. The mission of the Global SIPI University will be to give students, technicians, and engineers the opportunity to acquire SI & PI skills directly from experienced and well-known instructors from both industry and academia.

The program offers both lectures and practical demonstrations. The intent is to expand the discussion on the background concepts and to provide a more detailed presentation of advanced methods for addressing the current design challenges. Moreover, the demos will encompass the use of instruments typically employed for analysis, measurement and troubleshooting for signal and power integrity.

MEET OUR CO-CHAIRS

Francesco de Paulis

University of L’Aquila, L’Aquila, Italy

Francesco de Paulis (Senior Member IEEE) received the M.S. degree in Electrical Engineering in May 2008 from Missouri University of Science and Technology (formerly University of Missouri-Rolla), USA, and the Ph.D. degree in Electrical and Information Engineering in 2012 from the University of L’Aquila, L’Aquila, Italy. He is currently an Associate Professor at the Electromagnetic Compatibility and Signal Integrity Laboratory at the University of L’Aquila. His main research interests are in signal and power integrity, high speed channel design and optimization, composite materials for shielding and absorption, RF interference in mixed-signal system, TSVs in silicon chips and interposers, antenna design and measurement techniques, remote fault detection in transmission lines, microwave design of electronic devices and systems for space applications.

Majid Ahadi Dolatsara

Keysight Technologies

Majid Ahadi Dolatsara received the B.Sc. degree in electrical engineering from the K.N.Toosi University of Technology, Tehran, Iran, in 2013, and the M.Sc. degree in electrical engineering from the Colorado State University, Fort Collins, CO, USA, in 2016. He received the Ph.D. degree in electrical and computer engineering with a minor in computer science from the Georgia Institute of Technology, Atlanta, GA, USA in 2021, where he focused on development of machine learning based electronic design automation (EDA) tools for signal integrity and high-speed channels.

He has been with Keysight Technologies, Calabasas, CA, USA, since 2021, where he currently works as a senior machine learning R&D engineer developing ML-based modeling and optimization tools for EDA.

MEET OUR INSTRUCTORS

TUESDAY, AUGUST 4, 2026

Opening Session:

Overview of High-Speed Signal Integrity (SI)

Bhyrav Mutnury

AMD, Austin, TX, USA

ABSTRACT

In this presentation, a brief history and overview of Signal Integrity (SI) are discussed. The session navigates the transition of SI from low-speed board designs to multi-gigabit AI hardware, emphasizing how increased frequencies have redefined the physics of interconnects. Finally, the discussion identifies modern high-speed bottlenecks and the unique opportunities they bring to the future of design.

ABOUT BHYRAV MUTNURY

Bhyrav Mutnury is a Senior Fellow at AMD, part of Technology and Engineering division where he is responsible for high-speed signal integrity. Prior to this, Dr. Mutnury was a Senior Distinguished Engineer and Global Team Leader of Signal Integrity group at Dell Technologies. He received his Doctor of Philosophy degree in Electrical Engineering in 2005 from the Georgia Institute of Technology, Atlanta, GA. Dr. Mutnury has authored more than 100 publications in various conferences and journals. Dr. Mutnury has 300 issued patents and another 50 in the pipeline. He is currently an IEEE Fellow and the recipient of IEEE Technical Achievement Award.

Introduction to SI and PI: Evolution from the Basics to the Current Technology

Francesco De Paulis

University of L’Aquila, L’Aquila, Italy

ABSTRACT

This presentation will introduce the concepts of signal and power integrity, and the evolution, in the past two decades, of the challenges associated with the modeling, analysis, and design of high speed interconnects and high-current PDNs. An overview of the current trends based on the state of the art of the technology discussed in the following sessions will be given.

ABOUT FRANCESCO DE PAULIS

Francesco de Paulis received the M.S. degree in Electrical Engineering in May 2008 from Missouri University of Science and Technology (formerly University of Missouri-Rolla), USA, and the PhD degree in Electrical and Information Engineering in 2012 from the University of L’Aquila, L’Aquila, Italy.

He is currently an Associate Professor at the Electromagnetic Compatibility and Signal Integrity Laboratory, University of L’Aquila, Italy, and an Adjunct Professor at the Missouri University of Science and Technology.

His main research interests are in signal and power integrity, high speed channel design, electromagnetic compatibility, antenna design and measurement techniques, design of electronic devices and systems for space applications

Transmission Line Effects, Lumped Effects, Passive Interconnect Design, Terminations and Reflections

John Golding

Siemens EDA, Livonia, MI, USA

ABSTRACT

In this session we will discuss signal integrity effects and design considerations of passive interconnects. Understanding the effects channels have on signals is critical to designing for signal integrity, and designing for signal integrity is critical for product design. Concepts including lumped and transmission line effects, reflections, and terminations will be presented and illustrated with examples. A grasp of these fundamental concepts enables engineers to solve many signal integrity challenges and is a foundation for learning additional, and more advanced topics in signal integrity.

ABOUT JOHN GOLDING

John Golding is a Senior Applications Engineer Consultant with Siemens EDA. He has been working with engineers in several industries for over 10 years to solve their Signal and Power Integrity analysis challenges. Prior to his current role, he was a hardware engineer for 18 years where he was responsible for the design, analysis, and verification of high-speed communications products. He holds a BSEE degree from the University of Michigan and MSEE degree from Illinois Tech.

Signal Integrity II: How Interconnects Work: The Physics of Losses, Reflections, and Coupling

Yuriy Shlepnev

Simberian Inc., Venice, CA, USA

ABSTRACT

At data rates exceeding 112 Gbps, interconnects function as waveguides where energy travels in the dielectric space, not merely on the traces. This session explores the fundamental physics of signal degradation to demystify high-speed interconnect behavior. We will examine the anatomy of material losses, visualizing how dielectric polarization and conductor surface roughness dissipate energy. The discussion progresses to reflections, treating discontinuities—specifically vias—as vertical waveguides with distinct radiation properties. Finally, we analyze crosstalk through the lens of electromagnetic field coupling and modal velocity differences. By shifting focus from simple circuit equations to physical field behavior, attendees will gain the insight needed to predict performance and mitigate signal integrity issues in next-generation designs.

ABOUT YURIY SHLEPNEV

Yuriy Shlepnev is the founder and president of Simberian Inc., creator of Simbeor—an industry‑leading electromagnetic signal‑integrity platform used by system design teams worldwide. He is the original architect of Simbeor’s physics‑based solvers, material‑model extraction methods, and high‑frequency interconnect analysis workflows. With four decades in applied electromagnetics, Yuriy has contributed algorithms, measurement‑correlation techniques, and practical methodologies that shaped modern SI engineering. His recent work includes bringing AI‑driven automation and reproducibility to EM analysis through Simbeor Commander, enabling scalable pre‑ and post‑layout workflows for enterprise design teams.

WEDNESDAY, AUGUST 5, 2026

Signal Integrity III: S-params In the Eyes of the Beholder: Interconnect Design Considerations at 224 Gb/s and 448 Gb/s

Brandon T. Gore

Samtec Inc, Columbia, SC, USA

ABSTRACT

The latest trends in SI design require an understanding from basic interconnect design challenges through to how the DSP receivers correct interconnect distortions. PCB stackup design choices have tradeoffs that impact loss, routing density, and vertical transitions. These vertical transitions, especially, have negative impacts on the breakout region (BOR) connector performance targets that go along with mechanical requirements for mating of the connector. However, signaling is ultimately in the time domain, and it can be helpful to use single bit responses of the channel to understand the limits of equalization on ISI. Additionally, modulation choices such as Pulse Amplitude (PAM4 or PAM6) tighten the requirements on SNR. The presentation introduces the above subjects, and it shares tips specific to the design of interconnect component evaluation for 224 Gb/s signaling, and a look toward barrier of 448 Gb/s.

ABOUT BRANDON T. GORE

Brandon T. Gore is presently a Principal Technologist and Director at Samtec managing both the Signal Integrity R&D and Electronic Industry Standards teams. His research focuses are advanced interconnect materials, characterization methodologies, active linear cables, and general signal integrity bottlenecks for 400Gbps data rates. He is an active contributor to both IEEE 802.3, SFF-TA-1043, and OIF Common Electrical I/O projects. Brandon received the PhD degree in electrical engineering from the University of South Carolina under Dr. Paul G. Huray.

Signal Integrity IV: Measurements for Signal Integrity (VNA and TDR)

Matteo Cocchini

IBM, Poughkeepsie, New York, USA

ABSTRACT

This presentation aims to provide a comprehensive introduction to the fundamental principles behind Vector Network Analyzer (VNA) and Time Domain Reflectometer (TDR) measurements. The session will begin by covering the core theoretical concepts that support these instruments, followed by illustrative practical examples based on real designs.

For the VNA, in addition to the standard extraction of S-parameters, the discussion will emphasize advanced techniques, such as calibration processes, embedding and de-embedding methods, and the presentation of real-world data. Meanwhile, the TDR portion of the lecture will delve into its essential principles, explore its common industrial applications, and address frequent challenges and potential issues that SI engineers could encounter in test environments.

ABOUT MATTEO COCCHINI

Matteo Cocchini (M’18) received his Laurea in Electronic Engineering in June 2006 from University of L’Aquila, L’Aquila, Italy. He received the Master of Science in Electrical Engineering from Missouri University of Science and Technology, Rolla, MO in May 2008.

Matteo is author or co-author of more than 50 conference and journal papers in the fields of PI and SI and holds more than 40 patents, filed or pending.

He is an IBM Master Inventor and a senior engineer, team leader of the IBM Z I/O signal and power integrity development team, Poughkeepsie, New York.

Keynote: Powering AI Performance from Silicon to System: The Role of SIPI

Barry Katz

MathWorks, Natick, MA, USA

ABSTRACT

As large AI models grow from billions to trillions of parameters, performance on AI training and inference is no longer constrained by compute capability alone, but by memory bandwidth, high-speed interconnects, and robust power delivery. This keynote examines how signal integrity (SI) and power integrity (PI) shape next-generation AI platforms—from die-to-die links in chiplet packages and co-packaged optical interconnects to low-impedance, high-efficiency power delivery networks that support highly dynamic workloads.

We will explore why SIPI is evolving from a post-design verification task into a system-level design discipline. The talk will also highlight emerging analysis methodologies and automation frameworks—including agentic, AI-driven approaches—that are accelerating SI/PI analysis and enabling scalable design of increasingly complex, high-performance AI compute platforms.

ABOUT BARRY KATZ

Barry Katz, Director of Engineering, RF & AMS Products, leads the development teams responsible for RF, EM, Signal Integrity, SerDes, and Mixed-Signal modeling and simulation products at MathWorks. Before joining MathWorks, Barry served as President and CTO of SiSoft which he founded in 1995. At SiSoft, Barry was responsible for leading the definition and development of SiSoft’s products. He has devoted much of his career to delivering a comprehensive design methodology, software tools, and expert consulting to solve the problems leading-edge high-speed systems designers face. Barry was the founding chairman of the IBIS Quality Committee. He received his B.S.E.E. from the University of Florida and his M.S.E.C.E. from Carnegie Mellon.

Signal Integrity Demo 1: Time Domain Properties of Transmission Lines

Eric Bogatin

University of Colorado, Boulder, CO, USA

ABSTRACT

All interconnects are transmission lines. We hear about their properties and simulate their effects in various EM or circuit simulator tools. In this demonstration, you will see the impact of transmission line properties. We will use a low-cost scope and low-cost TDR to show five examples of important properties of transmission lines in the real world. The test boards we will measure are commercially available open-source boards available to anyone. Using these tools and methods, you can replicate these measurements at your facility. These demonstrations include: the time of flight of signals, the instantaneous impedance and reflections with a TDR, how to reduce reflections in scope measurements and measuring the output impedance of a driver using a scope.

ABOUT ERIC BOGATIN

Eric Bogatin received his BS in Physics from MIT in 1976 and PhD in Physics from the University of Arizona in 1980. He has been active in the SI field for 40 years and has written 15 books and hundreds of articles in this field. Currently, he teaches SI and Electronics courses for undergraduate and graduate students. He is also a Fellow with Teledyne LeCroy.

Signal Integrity V: Simulation and Modeling of Signal Integrity for High-Speed Wired Communications.

Renato Rimolo-Donadio

Instituto Tecnológico de Costa Rica, Cartago, Costa Rica

ABSTRACT

High-speed wired interfaces are the backbone of modern electronic systems, facilitating critical data transfer for memory, peripherals, networks, and even chiplets, at speeds exceeding 200 Gb/s per lane. Achieving these data rates requires rigorous co-optimization of interconnect channels and transceiver circuits, addressing factors such as package design, signaling schemes, equalization, coding, and energy efficiency. Given the hundreds of tunable parameters and the complex coupling between channels and power domains, design optimization is a significant challenge. This talk reviews the state-of-the-art modeling approaches and abstractions necessary for comprehensive end-to-end analysis of signal integrity in next-generation high-speed links, considering full-wave or hybrid methods to describe the channel, and circuit simulation or behavioral models for analysis including the transceiver circuits.

ABOUT RENATO RIMOLO-DONADIO

Renato Rimolo-Donadio received the B.S. in Electrical Engineering from the Instituto Tecnológico de Costa Rica (ITCR) in 2004, M.Sc. and Ph.D. degrees from the Technische Universität Hamburg (TUHH), Germany, in 2006 and 2010, respectively. He was with the Institute of Electromagnetic Theory at TUHH (2006–2012), and with the IBM Thomas J. Watson Research Center in New York (2012–2014). Since 2014, he has served as a Full Professor in the Department of Electronics Engineering at ITCR. From 2021 to 2024 he was Senior Analog Engineer with Intel Costa Rica, and from 2024 he has been with the Rydev ASIC Design House as Engineering Manager. His primary research interests encompass high-speed integrated circuit design, power and signal integrity, and the system-level modeling and optimization of interconnects.

Signal integrity Demo II: Frequency Domain – VNA (calibration and channel analysis)

Paul Peterson

Rohde & Schwarz, Dallas, TX, USA

ABSTRACT

This presentation expands on prior VNA-based signal integrity analysis with advanced time-domain and simulation techniques. The live demo highlights differential measurements on high-speed interconnects, extracting mixed-mode S-parameters to assess differential insertion loss, return loss, and mode conversion in balanced serial links.

Attendees will see real-time eye diagram generation from S-parameters, evaluating eye height, width, jitter, and noise. Simulated throughput analysis predicts data rates and margins under equalization scenarios. Automated report generation streamlines documentation of de-embedded results, eye overlays, and compliance metrics.

Enhanced calibration and de-embedding ensure precision in complex setups. This hands-on session equips engineers with cutting-edge tools to optimize high-speed designs and accelerate validation.

ABOUT PAUL PETERSON

Paul Peterson is a VNA Product Planning Engineer within the R&D department at Rohde & Schwarz, bringing a wealth of expertise garnered from his extensive experience in the telecom, defense, and semiconductor design industries. Prior to his current role, he spent over six years providing comprehensive support for the entire range of RF products at Rohde & Schwarz. During that time as an application engineer he used his ability to distill complex technologies into accessible insights. Mr. Peterson frequently engages with large, diverse groups through keynote presentations and in-depth training sessions. As a member of the forward-looking planning team, Mr. Peterson is now responsible for aligning Rohde & Schwarz’s VNA platforms with the evolving needs of both current and future customers.

Signal Integrity VI: Unmasking The DUT: Fixture De-Embedding Essentials

Giorgi Maghlakelidze

NVIDIA, Santa Clara, CA, USA

ABSTRACT

As high-speed digital designs push the technological boundaries, characterizing the interconnects accurately becomes more important. What does it mean “accurate enough” and how to achieve it? The test fixtures introduce measurement errors that mask true device performance both in frequency and time-domain characteristics. This presentation aims to equip the audience with practical fixture de-embedding skills, covering not only the fundamentals, but also practical design, the IEEE 370 standard methods, quality metrics and approach selection.

Aside from theory and best practices, several real-world case studies are used to illustrate common pitfalls in single-ended and differential de-embedding. An anonymized tools comparison examines several common commercial solutions alongside open-source implementations (such as IEEE 370 reference MATLAB code or its Python adaptation) with practical code examples the audience can follow along, or examine at their leisure. Attendees will leave equipped to implement and validate robust de-embedding workflows.

ABOUT GIORGI MAGHLAKELIDZE

Giorgi Maghlakelidze, PhD is a Senior Signal and Power Integrity Engineer at NVIDIA Corporation, where he develops SI solutions for high-speed links including NVLink-C2C for the latest AI Infrastructure platforms. Previously, he served as Senior SIPI Engineer at Cisco Systems (2020-2024), driving system development for C9400 Catalyst Enterprise Switches from feasibility through post-fab validation, and system integration for SiliconOne ASIC. Giorgi earned his PhD in Electrical Engineering from Missouri University of Science and Technology in 2020. He has authored numerous IEEE publications, including work on glass weave skew effects, and serves as an Officer-at-large for the IEEE EMC Society TC-10 on Signal and Power Integrity. A firm believer that simulation must be verified through measurement, he strives to correlate the models to lab data to understand his designs. He advocates for open-source tools in the SI/PI community and co-chairs the “When Open Source Meets SIPI” workshop at the IEEE EMC+SIPI Symposium.

Power Integrity I: Power Integrity Fundamentals

Dan Chirpich

Rochester, NY, USA

ABSTRACT

What does power integrity mean? Why does power have decoupling capacitors? What makes a vendor’s, reference design’s, or senior engineer’s recommendations correct (or not)? If one is relying on commonly used decoupling strategy because ‘it works’ or ‘is proven’, does that mean the design has ‘good enough’ power integrity?

This session will focus on fundamentals that equip attendees with engineering basis to answer these questions for themselves. A high-level example of a power integrity workflow applying the fundamentals will be presented. Content will apply from the simplest embedded microcontrollers, to highly sensitive modern RF designs, to modern data center chips that draw thousands of amps into 700 – 900 mV core power.

ABOUT DAN CHIRPICH

Dan Chirpich is a Principal Engineer at Re:Build AppliedLogix, LLC, a Rochester, NY-based custom embedded electronics and software design firm. Dan leads their signal and power integrity design services supporting a wide range of OEM customers in multiple industries. His work spans a broad range of design complexity – from MHz-rate multi-drop signal quality analysis to terabit-throughput system interconnect. His power integrity analysis work spans from review for low impedance design to delivering milli- to micro-ohm-range flat impedance PDNs with time domain sign-off.

Dan has been a practicing engineer for 20 years. He now focuses on his unequivocal engineering passion – signal and power integrity; however, he enjoyed equal amounts of project, hardware, and FPGA engineering roles in the past. He’s earned three engineering degrees from the University of Kansas.

THURSDAY, AUGUST 6, 2026

Power Integrity II: VRM Basics, VRM Modeling, and IR Drop

Chulsoon Hwang

Missouri S&T, Rolla, MO , USA

ABSTRACT

For end-to-end power integrity simulation and analysis, it is essential to include and understand voltage regulator modules (VRMs), which are a key component of the power distribution network. This presentation covers the fundamentals of VRMs, their frequency domain and time domain behavior, simulation models, and considerations for sensing point in PCB PDN design, with practical examples.

ABOUT CHULSOON HWANG

Chulsoon Hwang is an Associate Professor at Missouri S&T. He has authored or co-authored more than 200 IEEE journal/conference papers. His research interests include High-speed Digital System Design, RF Desensitization, and Machine Learning-assisted Hardware Design. He has received 13 Best Paper Awards from various international conferences including IEEE EMC+SIPI and DesignCon.

Power Integrity III: Package and IC PDN, On-Chip VRM

Michael J. Hill

Intel Foundry. Chandler, Arizona, USA

ABSTRACT

To provide competitive compute performance, today’s high-power CPUs and GPUs often consume many hundreds or even thousands of watts of power. PDNs for these products must provide low noise power despite unimaginably large and fast transient loads. This frequently requires the use of advanced power delivery solutions like package embedded capacitors, on die MIM capacitors and integrated voltage regulators. Additionally, some of these building blocks also rely on their own downstream set of advanced technologies like high performance integrated magnetics. This presentation will provide an overview of some of these technologies including how and why they are used. An introduction to some of the design tradeoffs, cost implementations, manufacturing difficulties and validation challenges will be presented.

ABOUT MICHAEL J. HILL

Michael J. Hill is a Principal Engineer with Intel’s Electrical Core Competency group where he has been since 2002. His work includes the development of new tools and techniques to allow precise characterization of substrate electrical performance metrics spanning PD, HSIO and RF applications. Much of his recent work has focused on metrologies for characterizing integrated voltage regulators. He is also responsible for developing characterization methods for package material sets spanning DC to 130GHz, and methods for characterizing mmWave package antennas. Michael is a senior member of the IEEE, has authored more than 30 peer reviewed publications and has been granted more than 15 patents. He holds B.S., M.S. and Ph.D. degrees in Electrical Engineering from the University of Arizona.

Power Integrity Demo I: Measurements Low Impedance PDN

Benjamin Dannan

Signal Edge Solutions, Baltimore, MD, USA

ABSTRACT

Modern high-speed electronic systems, particularly those employing advanced ASIC and chiplet packages for AI and data center applications, face critical challenges in managing power delivery network (PDN) integrity. High current densities, coupled with higher power rail density on the package and demanding data rates, contribute to significant challenges. While PDN impedance is a key metric, measuring high-current PDNs (e.g., 2000A) presents difficulties, notably ground loop errors in 2-port measurements. Employing ground loop isolators with adequate Common-Mode Rejection Ratio (CMRR) is crucial. This presentation will demonstrate a practical approach to accurately measure a 2000-Amp (or 40 µΩ) PDN using various VNAs. We will detail how to determine the minimum CMRR needed for reliable 2-port probe measurements and show that sub-40 µΩ impedance measurements are achievable with isolators possessing sufficient CMRR.

ABOUT BENJAMIN DANNAN

Benjamin Dannan is the Founder and Chief Technologist at Signal Edge Solutions. Benjamin Dannan is an experienced signal and power integrity (SI/PI) design consultant developing advanced packaging solutions for high-performance ASICs, chiplets, and complex FPGA designs. He is a Keysight ADS Certified Expert with expert-level proficiency in high-speed simulation solutions and multiple 3D EM solutions. He has expert-level proficiency with multiple test and measurement solutions, including oscilloscopes, vector network analyzers (VNA), Time Domain Reflectometers (TDRs), function generators, and EMC lab testing equipment.

Closing Session: Understanding Vias for Better SI and PI – 50+ Years of Physics-Based Modeling

Christian Schuster

Hamburg University of Technology (TUHH), Hamburg, Germany

ABSTRACT

Vias on printed circuit boards are essential structures for signal interconnects and power delivery networks. As they traverse the metallic and dielectric layers of the board they give rise to fascinating effects, most notably the excitation of parallel plate modes. Understanding the physics of these modes – which actually constitute the displacement return current distribution – is essential to understanding and optimizing vias for both signal and power integrity. In this contribution to the GU SIPI we will follow a 50+ years journey of physics-based modeling of vias on PCBs starting with the famous paper of Takanori Oksohi on planar circuits in 1972. We will end with discussing current approaches that are making the transition from purely physics-based to physics+data-based.

ABOUT CHRISTIAN SCHUSTER

Christian Schuster (IEEE Fellow) received a Diploma degree in physics and a Ph.D. degree in electrical engineering. Since 2006 he is a full professor at Hamburg University of Technology (TUHH), Germany. Prior to TUHH he was with the IBM T. J. Watson Research Center, Yorktown Heights, NY, USA. His interests include signal and power integrity of digital systems, multiport measurement and calibration techniques, and development of physics-based as well as data-based modeling, simulation and optimization methods for EMC+SIPI. In the recent past, he has served as an Associate Editor for the IEEE Transactions on EMC, as an Adjunct Associate Professor at the School of Electrical and Computer Engineering of the Georgia Institute of Technology, and as a co-founder of the Global Signal Integrity and Power Integrity University (GU SIPI).